- rev.f0は、FPGA上で直接実装することを念頭において設計された命令セットです。

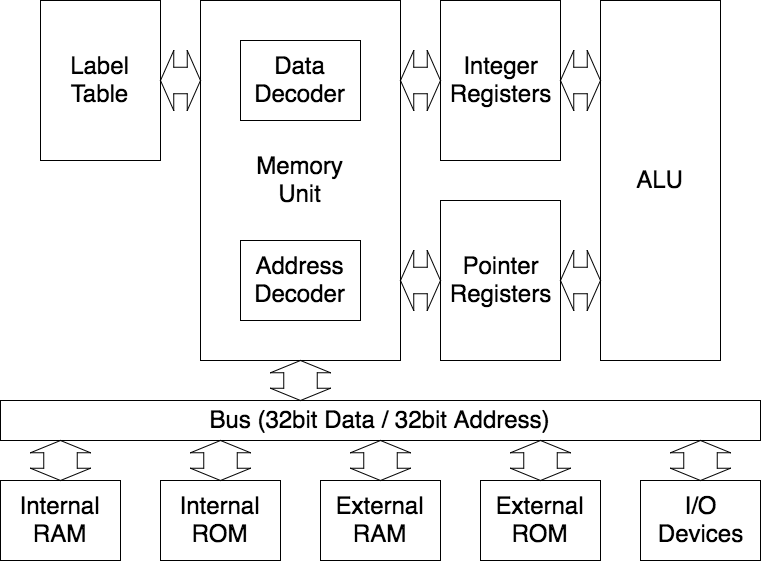

- OSECPUは「セキュリティを重視した命令セット」と「バイトコード密度」が主要な特徴であるから、これを直接サポートしたCPUを実装する。

- この命令セットは4ビット単位なので、4ビット単位のメモリアクセスをハードウエアでサポートしたい。

- ラベル位置にしか飛べない。データはもちろん実行できない。

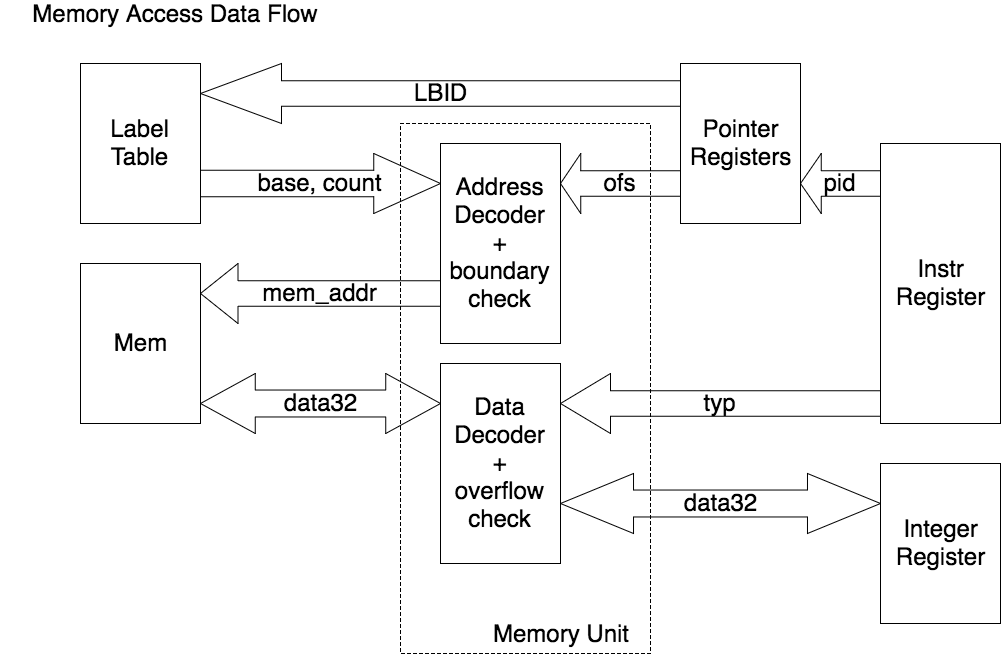

- メモリアクセス時の範囲チェックおよびタイプチェックを強制する。

- バイトコードには複数のレベルがある。

- CPUで直接可変長(hh4)エンコードの命令を実行するのは効率が悪い。

- そこで、CPUの命令セットとしては固定長のものを新たに設計する。

- ただし、CPUに入力する命令セットとしては、可変長のバックエンドコード(すでに設計されているもの)を採用する。

- ラベルのみにジャンプできる

opcode.mdを参照。

- 電源投入後はROMの変換プログラム(位置と範囲は予め設定しておく)が実行される。

- 電源投入直後のローダ実行用に、CPUは一定のメモリ範囲をコード領域としてラベルテーブルに追加する。

- その後、ローダがRAM上のバックエンドコードを読み込んで、CPUコードに変換して展開する。

- ラベルテーブルへ追加する命令(LBSET)もローダが生成する。(プログラム本体の実行に先立って実行される。)

- 詳細についてはback2cpu.mdを参照のこと。